# 650V N-Channel MOSFET

#### **General Description**

This Power MOSFET is produced using advanced planar stripe DMOS technology. This advanced technology has been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode. These devices are well suited for high efficiency switched mode power supplies, active power factor correction based on half bridge topology.

#### Features

7A, 650V, RDS(on)typ. = 1.65Ω@VGS = 10 V Advanced planar process Low gate charge minimize switching loss Fast switching 100% avalanche tested Improved dv/dt capability

| Symbol           | Parameter   Drain – Source Voltage              |              |               | JFFC7N65E   | Units |

|------------------|-------------------------------------------------|--------------|---------------|-------------|-------|

| VDSS             |                                                 |              |               | 650         | V     |

| lo               | Drain Current                                   | Continuous ( | Tc = 25 °C )  | 7*          | А     |

|                  | Drain Current                                   | Continuous ( | Tc = 100 °C ) | 4*          | А     |

| DM               | Drain Current - F                               | Pulsed       | ( Note 1 )    | 25          | А     |

| Vgss             | Gate – Source Voltage                           |              |               | ±30         | V     |

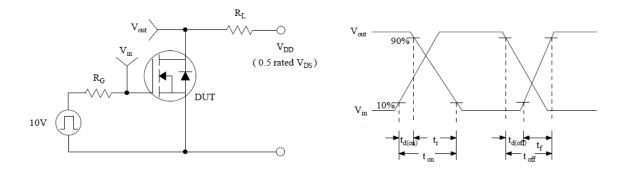

| EAS              | Single Pulsed Avalanche Energy (Note 2)         |              | ( Note 2 )    | 106         | mJ    |

| Iar              | Avalanche Current                               |              | ( Note 1 )    | 7           | А     |

| Ear              | Repetitive Avalanche Energy                     |              | ( Note 1 )    | 10          | mJ    |

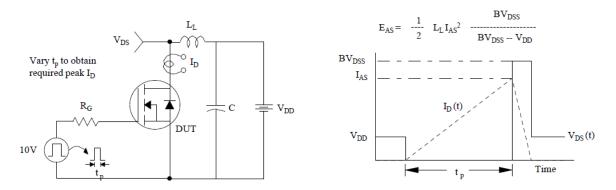

| dv/dt            | Peak Diode Recove                               | ery dv/dt    | ( Note 3 )    | 5.0         | V/ns  |

| PD               | Power Dissipation ( $T_c = 25 \degree C$ )      |              |               | 43          | W     |

|                  | -Derate above 25 °C                             |              |               | 0.34        | w/°C  |

| TJ <b>,</b> Tstg | Operating and Storage Temperature Range         |              |               | -55 to +150 | °C    |

| Τι               | Maximum lead temperature for soldering purposes |              |               | 300         | °C    |

|                  | 1/8" frome case for 5 seconds                   |              |               | 300         |       |

#### Absolute Maximum Ratings Tc = 25 °C unless otherwise noted

\*Drain current limited by maximum junction temperature.

### **Thermal characteristics**

| Symbol | Parameter                               | JFFC7N65E | Units |

|--------|-----------------------------------------|-----------|-------|

| RθJC   | Thermal Resistance, Junction-to-Case    | 2.9       | °C/₩  |

| Reja   | Thermal Resistance, Junction-to-Ambient | 62.5      | °C/W  |

#### **Electrical Characteristics** Tc = 25 °C unless otherwise noted

| Symbol            | Parameter                                         | Test Conditions                                                    | Min | Тур  | Max  | Units |

|-------------------|---------------------------------------------------|--------------------------------------------------------------------|-----|------|------|-------|

| Off Charact       | eristics                                          | ·                                                                  |     | •    | •    |       |

| BVDSS             | Drain – Source Breakdown Voltage                  | V <sub>GS</sub> = 0 V, I <sub>D</sub> = 250 uA                     | 650 |      |      | V     |

| ⊿ BVdss/<br>⊿TJ   | Breakdown Voltage Temperature<br>Coefficient      | I <sub>D</sub> = 250 uA, Referenced to 25 °C                       |     | 0.5  |      | v/℃   |

| IDSS              |                                                   | V <sub>DS</sub> = 650 V, V <sub>GS</sub> = 0 V                     |     |      | 1    | uA    |

|                   | Zero Gate Voltage Drain Current                   | V <sub>DS</sub> = 520 V, Tc = 125 ℃                                |     |      | 10   | uA    |

| Igssf             | Gate-Body Leakage Current, Forward                | V <sub>GS</sub> = 30 V, V <sub>GS</sub> = 0 V                      |     |      | 100  | nA    |

| GSSR              | Gate-Body Leakage Current, Reverse                | V <sub>GS</sub> = -30 V, V <sub>GS</sub> = 0 V                     |     |      | -100 | nA    |

| On Charact        | eristics                                          |                                                                    |     |      |      |       |

| VGS(th)           | Gate Threshold Voltage                            | V <sub>DS</sub> = V <sub>GS</sub> , I <sub>D</sub> = 250 uA        | 2.0 |      | 4.0  | V     |

| RDS(on)           | Static Drain-Source on-Resistance                 | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 3.5A                      |     | 1.65 | 1.8  | Ω     |

| <b>g</b> FS       | Forward Transconductance                          | V <sub>DS</sub> = 40 V, I <sub>D</sub> = 7 A (Note 4)              |     | 10   |      | S     |

| Dynamic Ch        | naracteristics                                    |                                                                    |     |      |      |       |

| Ciss              | Input Capacitance                                 |                                                                    |     | 680  |      | pF    |

| Coss              | Output Capacitance                                | $V_{DS} = 25 V, V_{GS} = 0 V, f = 1.0 MU_{T}$                      |     | 70   |      | pF    |

| Crss              | Reverse Transfer Capacitance                      |                                                                    |     | 8.4  |      | рF    |

| Switching C       | haracteristics                                    |                                                                    |     |      |      |       |

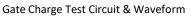

| td(on)            | Turn-On Delay Time                                |                                                                    |     | 12   |      | ns    |

| tr                | Turn-On Rise Time                                 | V <sub>DS</sub> = 325 V, I <sub>D</sub> = 7.0 A , R <sub>G</sub> = |     | 15   |      | ns    |

| td(off)           | Turn-Off Delay Time                               | $25\Omega$ , V <sub>GS</sub> = 10 V (Note 4,5)                     |     | 32   |      | ns    |

| tr                | Turn-Off Fall Time                                |                                                                    |     | 16   |      | ns    |

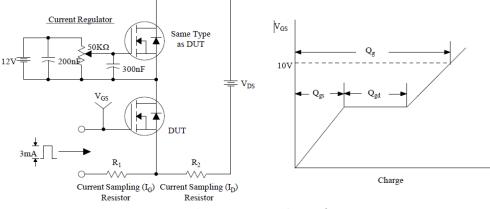

| Qg                | Total Gate Charge                                 |                                                                    |     | 17   |      | nC    |

| Qgs               | Gate-Source Charge                                | VDS = 480 V, ID = 7.0 A VGS =<br>10 V (Note 4,5)                   |     | 4    |      | nC    |

| $\mathbf{Q}_{gd}$ | Gate-Drain Charge                                 | 10 V (Note 4,5)                                                    |     | 7    |      | nC    |

| Drain – Sou       | rce Diode Characteristics and Maximum Ra          | tings                                                              |     |      |      |       |

| ls                | Maximum Continuous Drain-Source Diode             | Forward Current                                                    |     |      | 7    | Α     |

| lsм               | Maximum Pulsed Drain-Source Diode Forward Current |                                                                    |     |      | 25   | А     |

| Vsd               | Drain-Source Diode Forward Voltage                | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 7.0 A                      |     |      | 1.2  | V     |

| trr               | Reverse Recovery Time                             | V <sub>GS</sub> = 0 V, I <sub>S</sub> = 7.0 A                      |     | 300  |      | ns    |

| Qrr               | Reverse Recovery Charge                           | dlr/dt = 100 A/us (Note<br>4)                                      |     | 3.1  |      | uC    |

#### Notes:

1. Repetitive Rating : Pulsed width limited by maximum junction temperature

2. L = 4.0mH , Ias = 7A, V\_{DD} = 50V, R\_G = 25\Omega, Starting T\_J = 25  $^\circ \! C$

3.  $I_{SD} \leq 7.0A$ ,  $di/dt \leq 200A/us$ ,  $V_{DD} \leq BV_{DSS}$ ,  $Starting T_J = 25^{\circ}C$

4. Pulsed Test : Pulsed width  $\leq$ 300us, Duty cycle  $\leq$  2%

5. Essentially independent of operating temperature

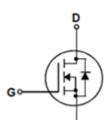

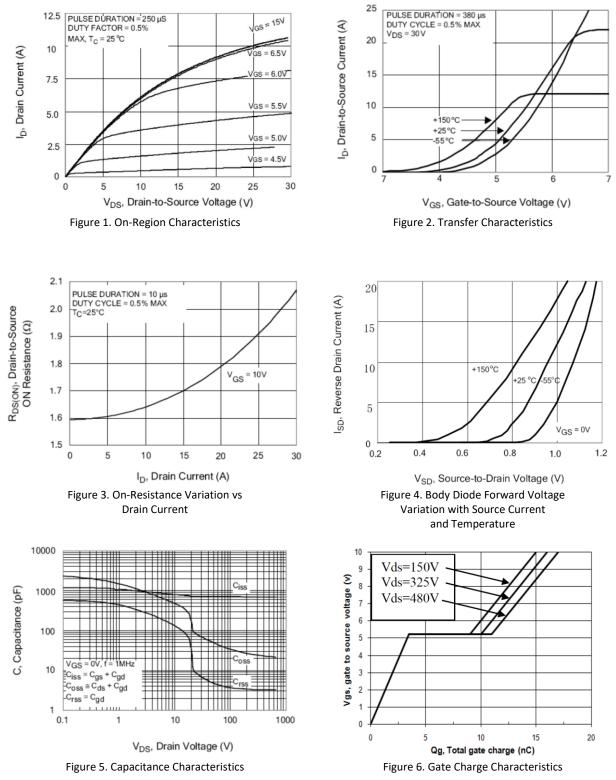

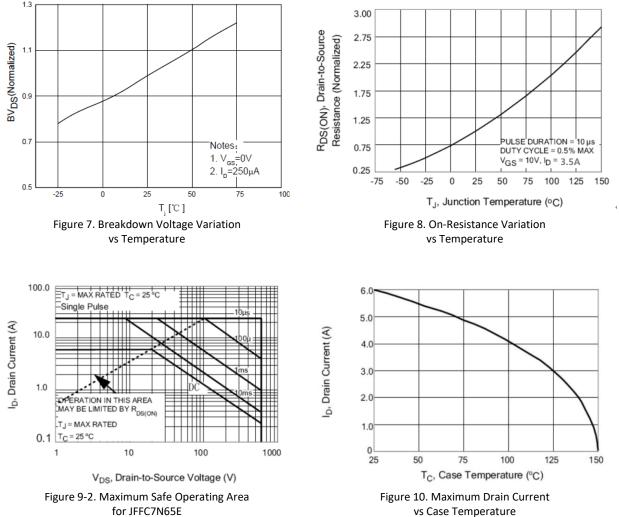

# **Typical Characteristics**

### **Typical Characteristics**

# **Typical Characteristics**

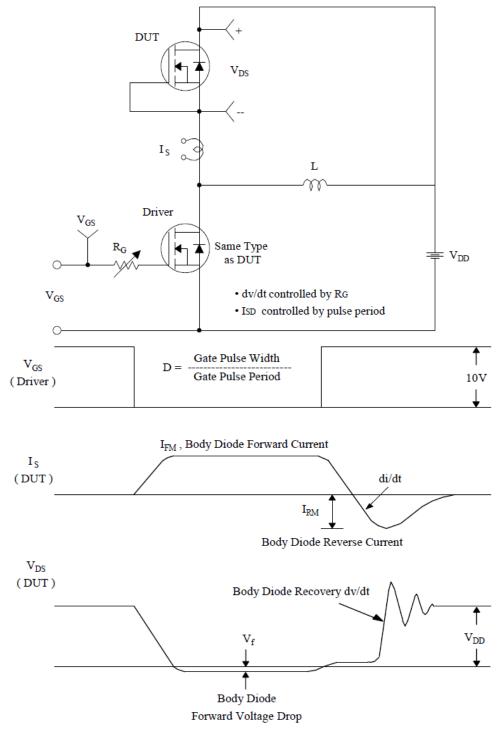

### Test Circuit & Waveform

Resistive Switching Test Circuit & Waveforms

Unclamped Inductive Switching Test Circuit & Waveforms

#### **Test Circuit & Waveform**

Peak Diode Recovery dv/dt Test Circuit & Waveforms

# **Disclaimers**

JIAEN Semiconductor Co., Ltd reserves the right to make changes without notice in order to improve reliability, function or design and to discontinue any product or service without notice. Customers should obtain the latest relevant information before orders and should verify that such information is current and complete. All products are sold subject to JIAEN's terms and conditions supplied at the time of order acknowledgement.

JIAEN Semiconductor Co., Ltd warrants performance of its hardware products to the specifications at the time of sale, Testing, reliability and quality control are used to the extent JIAEN deems necessary to support this warrantee. Except where agreed upon by contractual agreement, testing of all parameters of each product is not necessarily performed.

JIAEN Semiconductor Co., Ltd does not assume any liability arising from the use of any product or circuit designs described herein. Customers are responsible for their products and applications using JIAEN's components. To minimize risk, customers must provide adequate design and operating safeguards.

JIAEN Semiconductor Co., Ltd does not warrant or convey any license either expressed or implied under its parent rights, nor the rights of others. Reproduction of information in JIAEN's datasheets or data books sis permissible only if reproduction is without modification or alteration. Reproduction of this information with any alteration is an unfair and deceptive business practice. JIAEN Semiconductor Co., Ltd is not responsible or liable for such altered documentation.

Resale of JIAEN's products with statements different from or beyond the parameters stated by JIAEN Semiconductor Co., Ltd for that product or service voids all express or implied warrantees for the associated JIAEN's product or service and is unfair and deceptive business practice. JIAEN Semiconductor Co., Ltd is not responsible or liable for any such statements.